FRISC system-on-a-chip na FPGA razvojnoj pločici ULX2S

Uvod

Procesor

FRISC, dizajniran i razvijen

na FER-u unutar grupe

RASIP, može

se sintetizirati za rad na FPGA sklopovima različitih

proizvođača. Za razvojnu pločicu

FER-ULX2S

pripremljen je

system-on-a-chip sustav

temeljen na procesoru FRISC koji radi na taktu frekvencije 32.5 MHz.

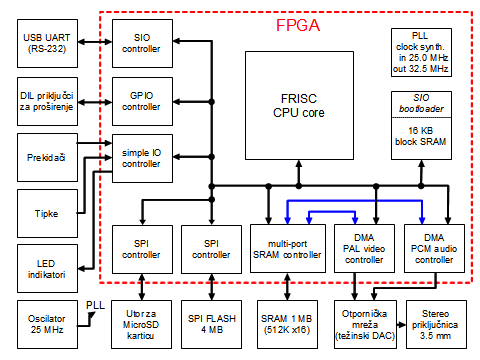

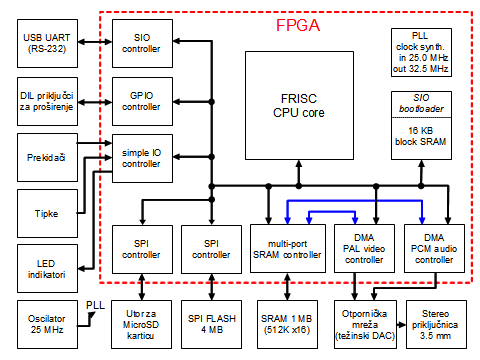

Moduli i priključci FRISC

system-on-a-chip

konfiguracije prikazani su blok shemom:

Nakon što se FPGA sklop konfigurira

odgovarajućom

bitstream datotekom,

izvršne programe za procesor FRISC moguće je putem USB

sučelja s računala učitati u mikroprocesorski sustav

na FPGA sklopu te ih pokrenuti korištenjem bilo kojeg programa

za emulaciju asinkronog terminala.

Konfiguriranje FPGA sklopa

Za konfiguriranje FPGA sklopa Lattice XP2 koristi se alat

ujprog

koji mora na računalo biti instaliran u kazalo C:\Windows

(za ostale operacijske sustave vidi

Upute

za rad s pločicom ULX2S). Zavisno od tipa

FPGA sklopa ugrađenog na razvojnu pločicu (Lattice XP2-5E

ili XP2-8E) potrebno je na računalo dohvatiti odgovarajući

konfiguracijski

bitstream

FPGA sklopa:

frisc_5e.jed

ili

frisc_8e.jed.

Primjer konfiguriranja FPGA sklopa s automatskim prelaskom na emuliranje

asinkronog terminala:

% ujprog -t frisc_8e.jed

ULX2S JTAG programmer v 2.beta0 $Id: ujprog.c 2683 2015-03-29 23:35:11Z marko $

Programming: 100%

Completed in 3.62 seconds.

Terminal emulation mode, using 115200 bauds

Press ENTER, ~, ? for help

|

Nakon pritiska na tipku ENTER pojavit će se

prompt

kontrolnog programa

(bootloader-a) procesora FRISC:

Prevođenje, učitavanje i pokretanje programa

Kontrolni program FRISC sustava

(bootloader) omogućuje

direktno učitavanje

i pokretanje izvršnih programa u formatu "

.p" koje stvara

assembler xconas.

Pri pokretanju assemblera kao prvi argument zadaje se put do

datoteke s opisom FRISC assemblera

frisc_v3ap1.adl,

a drugi argument je ime datoteke s izvornim kodom.

Primjer asembliranja izvornog koda pohranjenog u datoteci "prvi.asm":

% more prvi.asm

IO_LED EQU ffffff10

MOVE 0ff, R0

STOREB R0, (IO_LED)

RET

% xconas frisc_v3ap1.adl prvi.asm

|

Nakon završetka asembliranja program xconas može se prekinuti

pritiskom na CTRL+C. Izlazna datoteka imat će ekstenziju ".p".

Primjer assemblerskog izlaza ispitnog programa:

% more prvi.p

IO_LED EQU ffffff10

00000000 FF 00 00 04 MOVE 0ff, R0

00000004 10 FF 0F 98 STOREB R0, (IO_LED)

00000008 00 00 00 D8 RET

|

NOVO (2015)!!! Izvorni assemblerski kod može se prevesti

i korištenjem

eksperimentalnog online FRISC assemblera

u samo jednom koraku i bez potrebe za instaliranjem dodatnih programskih

alata na vlastito računalo!

Prevedeni program može se učitati u FRISC sustav na

FPGA pločici pomoću alata ujprog:

% ujprog -rta prvi.a

ULX2S JTAG programmer v 2.beta0 $Id: ujprog.c 2683 2015-03-29 23:35:11Z marko $

Using USB JTAG cable.

Reconfiguring FPGA...

Sending source.p: done.

Terminal emulation mode, using 115200 bauds

Press ENTER, ~, ? for help

FRISC @ 0000000C>

|

Alternativno, program se moze učitati utipkavanjem

prekidnog slijeda znakova u alatu ujprog:

(ENTER) ~ >

nakon čega treba upisati ime datoteke koju se šalje

putem USB sučelja:

FRISC @ 00000000>~>Local file name? prvi.p

|

Tijekom učitavanja datoteke u memoriju FRISC sustava treptat će LED

indikatori na razvojnoj pločici. Po završetku učitavanja treba još

jednom pritisnuti tipku ENTER, nakon čega bi na

promptu trebala

biti vidljiva adresa za jedan viša od adrese zadnjeg okteta učitanog

programa:

Prije pokretanja programa moguće je pregledati sadržaj memorije korištenjem

naredbe

examine (x):

FRISC @ 0000000C>x0

00000000 FF 00 00 04 10 FF 0F 98 00 00 00 D8 00 00 00 00 |................|

00000010 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

00000020 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

...

000000F0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

FRISC @ 00000100>

|

Program se pokreće naredbom

jump (j):

FRISC @ 00000100>j0

Booting at 00000000

FRISC @ 00000000>

|

U slučaju ispitnog programa

prvi.p na zaslonu se neće ispisati

nikakav tekst, ali će svi LED indikatori na razvojnoj pločici biti upaljeni.

Pokretanje programa s MicroSD kartice

Uz korištenje alternativne konfiguracije FPGA sklopa programe je u

FRISC sustav moguće automatski učitati i pokrenuti s MicroSD kartice.

Za pripremu sustava potrebno je najprije

ažurirati firmware na ugrađenoj Flash memoriji, nakon čega

FPGA sklop treba programirati posebno prilagođenom konfiguracijom FRISC-a

(

frisc_sd_5e.jed ili

frisc_sd_8e.jed, zavisno od varijante

ugrađenog FPGA chipa):

% ujprog -j flash frisc_sd_8e.jed

ULX2S JTAG programmer v 2.beta0 $Id: ujprog.c 2683 2015-03-29 23:35:11Z marko $

Using USB JTAG cable.

Programming: 100%

Completed in 27.11 seconds.

|

Na MicroSD karticu treba pohraniti pomoćni

program za učitavanje, te vlastiti program

za FRISC asembliran alatom xconas:

% cp frisc_ld.bin /cygdrive/e

% cp prvi.p /cygdrive/e

|

Uspostavom napajanja FPGA pločice (uključenjem u USB priključnicu

računala ili priključenjem na nezavisni izvor napajanja) FRISC sustav

će automatski učitati i pokrenuti program pohranjen na MicroSD kartici.

Inicijalizacija (reset) FPGA sklopa

U bilo kojem trenutku FPGA sklop se može inicijalizirati (resetirati)

utipkavanjem prekidnog slijeda znakova

ENTER,

~,

r

u alatu ujprog. Učinak tog postupka identičan je isključenju

te ponovnom ukapčanju FPGA pločice u računalo:

FRISC @ 00000000>x0

00000000 10 FF 8F 06 20 00 00 06 11 00 90 1C 00 00 D0 BC |.... ...........|

00000010 00 00 04 05 01 00 20 35 F8 FF 0F D6 01 00 40 36 |...... 5......@6|

00000020 E4 FF 0F D6 00 00 00 D8 00 00 00 00 00 00 00 00 |................|

00000030 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

...

000000F0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

FRISC @ 00000100>(ENTER ~ r, ne vidi se na ekranu!)

Reconfiguring FPGA...

Terminal emulation mode, using 115200 bauds

Press ENTER, ~, ? for help

ULX2S FAT bootloader v 0.4 (f32c/le) (built Mar 17 2015)

SIO bootloader v1.0

FRISC @ 00000000>x0

00000000 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

00000010 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

00000020 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

00000030 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

...

000000F0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 |................|

FRISC @ 00000100>

|

Unutarnji SRAM (FPGA block RAM)

Ukupno 16 KB unutarnje SRAM memorije ugrađne u FPGA sklop dostupno

je na adresnom rasponu od 0x00000000 do 0x00003FFF. Zadnjih 1 KB unutarnjeg

SRAMa, odnosno raspon od 0x00003C00 do 0x00003FFF, zauzima kontrolni

program

(bootloader) i taj se adresni raspon

ne smije koristiti u vlastitim programima.

Prilikom pokretanja učitanih programa

pokazivač stoga

(stack pointer) pokazivat će na

adresu 0x00003C00.

Vanjski SRAM

Na pločicu ULX2S ugrađena je statička RAM memorija (SRAM)

kapaciteta 1 MB.

U FRISC SoC sustavu ta memorija je dostupna na adresnom rasponu

od 0x80000000 do 0x800FFFFF. Osim procesora, memoriji putem odvojenih

sabirnica samostalno mogu pristupati grafički modul

(generator PAL video signala) te zvučni podsustav (PCM audio dekoder).

LED indikatori

Ukupno osam LED indikatora ugrađenih na razvojnu pločicu povezani

su na izlaz registra na adresi 0xFFFFFF10. Primjer pisanja u registar

LED indikatora u FRISC assembleru:

IO_LED EQU ffffff10 ; byte, WR

MOVE 0ff, R0

STOREB R0, (IO_LED)

|

Tipke i prekidači

Stanje signala povezanih s pet tipki i četiri DIP prekidača

na razvojnoj pločci može se pročitati na adresama

0xFFFFFF10 i 0xFFFFFF11. Primjer u FRISC assembleru povećat

će ili smanjiti vrijednost brojača u registru R4 ako su

pritisnute tipke BTN_UP odnosno BTN_DOWN, ili resetirati brojač

ako je pritisnuta tipka BTN_CENTER:

IO_PUSHBTN EQU ffffff10 ; byte, RD

IO_DIPSW EQU ffffff11 ; byte, RD

BTN_CENTER EQU 10

BTN_UP EQU 08

BTN_DOWN EQU 04

BTN_LEFT EQU 02

BTN_RIGHT EQU 01

LOAD R1, (IO_PUSHBTN) ; procitaj stanje tipki

AND R1, BTN_UP, R2 ; pritisnut btn_up?

JR_Z SKIP1 ; nije

ADD R4, 1, R4 ; povecaj brojac

SKIP1 AND R1, BTN_DOWN, R2 ; pritisnut btn_down?

JR_Z SKIP2 ; nije

SUB R4, 1, R4 ; smanji brojac

SKIP2 AND R1, BTN_CENTER, R2 ; pritisnut btn_center?

JR_Z SKIP3 ; nije

MOVE 0, R4 ; resetiraj brojac

SKIP3

|

Asinkrono serijsko sučelje

Komunikaciju između računala i FRISC SoC sustava

moguće je ostvariti putem asinkronog serijskog sučelja koje je

na FPGA pločici povezano s USB-UART premosnikom FTDI FT232R, a

omogućuje prijenos podataka brzinama između 300 i 3000000

bita u sekundi (standardna brzina prijenosa je 115200 bps).

Primjer rutina PUTCHAR i GETCHAR u FRISC assembleru

koje omogućuju pisanje odnosno čitanje znakova putem

asinkronog serijskog sučelja:

IO_SIO_BYTE EQU ffffff20 ; byte, RW

IO_SIO_STATUS EQU ffffff21 ; byte, RD

IO_SIO_BAUD EQU ffffff22 ; half, WR

SIO_TX_BUSY EQU 04

SIO_RX_FULL EQU 01

PUTCHAR ; salji char u R0 na RS232 port, kvari R1

LOADB R1, (IO_SIO_STATUS)

AND R1, SIO_TX_BUSY, R1 ; TX busy?

JR_NZ PUTCHAR ; je -> spin

STOREB R0, (IO_SIO_BYTE) ; posalji podatak

RET

GETCHAR ; u R0 vrati byte procitan sa RS232 porta

LOADB R0, (IO_SIO_STATUS)

AND R0, SIO_RX_FULL, R0 ; RX byte ready?

JR_Z GETCHAR ; nije -> spin

LOADB R0, (IO_SIO_BYTE) ; procitaj byte

RET

|

Grafički podsustav (PAL video)

Grafički modul nezavisno od procesora dohvaća podatke iz statičkog RAM-a

i 50 puta u sekundi osvježava prikaz slike rezolucije 512 * 288 točaka.

Izlazni kompozitni PAL video signal dostupan je na 3.5 mm stereo

priključnici razvojne pločice i može se bez ikakvih dodatnih prilagodbi

prikazati na svakom TV prijemniku ili zaslonu s kompozitnim video ulazom.

Linearni video

framebuffer može biti smješten u bilo

kojem dijelu vanjske statičke RAM memorije.

U upravljački registar na adresi 0xFFFFFF40 upisuje se kodna riječ

u kojoj dva bita najmanje težine određuju način rada grafičkog modula,

dok ostali bitovi određuju početnu adresu video

framebuffera.

Moguće je odabrati rad s 8-bitnim ili 16-bitnim kodiranjem boje svake

pojedine točke, uz korištenje fiksnih paleta.

|

|

|

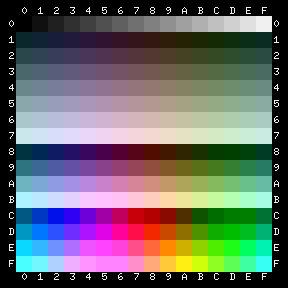

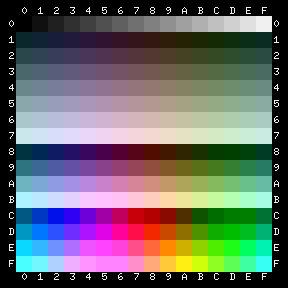

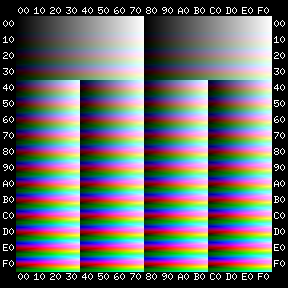

| 8-bitna paleta

|

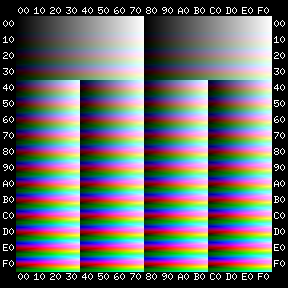

| 16-bitna paleta

|

Primjer podešavanja grafičkog modula za rad s 8-bitnim kodiranjem boje te

video

framebufferom na adresi 0x80010000, nakon

čega se nacrta dijagonalna crta u plavoj boji

koja se proteže od gornjeg lijevog

do donjeg desnog ruba ekrana:

IO_FB EQU ffffff40 ; word, WR

FB_MODE_8 EQU 00

FB_MODE_16 EQU 01

FB_MODE_TEST EQU 02

FB_MODE_OFF EQU 03

MOVE 8001, R1

SHL R1, 10, R1

STORE R1, (IO_FB) ; FB_MODE_8, FB base @ 80010000

MOVE 0c2, R0 ; plava boja

MOVE 120, R2 ; 288 redaka

LOOP

STOREB R0, (R1) ; pofarbaj pixel

STOREB R0, (R1 + 1) ; pofarbaj pixel

ADD R1, 202, R1 ; R1 += (512 + 2)

SUB R2, 1, R2

JR_NZ LOOP

RET

|

Dodatni primjer crtanja po video framebufferu - igra krizic-kruzic:

tic_tac_toe.asm

Zvučni podsustav (PCM audio)

Radom modula za generiranje zvučnog izlaza upravlja se putem četiri

registra. U registar IO_PCM_FIRST (0xFFFFFF50) upisuje se početna adresa

bloka u vanjskoj SRAM memoriji iz koje se DMA prijenosom u pravilnim

vremenskim intervalima dohvaćaju uzorci PCM audio signala, kodirani kao

parovi 16-bitnih vrijednosti. U registar IO_PCM_LAST (0xFFFFFF54)

upisuje se zadnja adresa DMA bloka. U registar IO_PCM_FREQ (0xFFFFFF58)

upisuje se frekvencija uzorkovanja izražena brojem ciklusa takta

frekvencije 32.5 MHz nakon kojih modul automatski DMA pristupom dohvaća

slijedeći uzorak PCM kodne riječi. U registar IO_PCM_VOLUME (0xFFFFFF5c)

upisuje

se glasnoća reprodukcije, odvojeno za lijevi i desni kanal u gornjih

odnosno donjih 16 bitova kodne riječi. Čitanjem registra IO_PCM_CUR

(0xFFFFFF50) može se odrediti trenutna vrijednost pokazivača

PCM uzoraka u DMA bloku.

Primjer: program u SRAM memoriju kopira osam PCM uzoraka koji

odgovaraju punom ciklusu sinusnog signala, podešava upravljačke

registre DMA modula, te u petlji "svira" C-dur ljestvicu različitim

brzinama reprodukcije.

IO_PCM_CUR EQU ffffff50 ; word, RD

IO_PCM_FIRST EQU ffffff50 ; word, WR

IO_PCM_LAST EQU ffffff54 ; word, WR

IO_PCM_FREQ EQU ffffff58 ; word, WR

IO_PCM_VOLUME EQU ffffff5c ; word, WR

IO_FB EQU ffffff40 ; word, WR

FB_MODE_OFF EQU 03

MOVE FB_MODE_OFF, R0 ; iskljuci signal video generatora, cime se

STORE R0, (IO_FB) ; na oba kanala stereo prikljucnice prospaja

MOVE 0ffffffff, R0 ; PCM audio izlaz

STORE R0, (IO_PCM_VOLUME) ; max. glasnoca zvuka na oba kanala

MOVE 8008, R1

SHL R1, 10, R1 ; R1 = 0x80080000 (pocetak DMA bloka)

STORE R1, (IO_PCM_FIRST) ; pocetna adresa DMA bloka

ADD R1, 1C, R2 ; zadnja adresa DMA bloka je 0x8008001C

STORE R2, (IO_PCM_LAST)

MOVE SIN_MAP, R0

MOVE 20, R2 ; kopiraj 32 bytes u vanjski SRAM (DMA blok)

COPY_LOOP

LOAD R3, (R0)

STORE R3, (R1)

ADD R0, 4, R0

ADD R1, 4, R1

SUB R2, 4, R2

JR_NZ COPY_LOOP

MOVE 7ffff, R4 ; brzina sviranja

SPEED_LOOP

MOVE PITCH_MAP, R2

MOVE 8, R3 ; 8 tonova ljestvice

PITCH_LOOP

LOAD R0, (R2) ; ucitaj iz tablice PITCH_MAP frekvenciju DMA

STORE R0, (IO_PCM_FREQ) ; upisi u registar IO_PCM_FREQ

ADD R2, 4, R2 ; pomakni pointer na sljedeci kod

MOVE R4, R0 ; unutarnja petlja za kasnjenje

DELAY SUB R0, 1, R0

JR_NZ DELAY

SUB R3, 1, R3 ; ponavljaj 8 puta

JR_NZ PITCH_LOOP

SHR R4, 1, R4

SHR R4, 1, R5

ADD R4, R5, R4

JR_NZ SPEED_LOOP

STORE R4, (IO_PCM_FREQ) ; upisi nulu u registar IO_PCM_FREQ

RET

SIN_MAP ; 8 stereo 16-bitnih PCM uzoraka

DW 00000000, 5a825a82, 7fff7fff, 5a825a82

DW 00000000, 0da82da82, 80008000, 0da82da82

PITCH_MAP ; code = Ftone * 8 * 2^24 / 32.5 MHz

DW %D 1080 ; C0 - 261.6 Hz

DW %D 1212 ; D0 - 293.6 Hz

DW %D 1361 ; E0 - 329.6 Hz

DW %D 1442 ; F0 - 349.2 Hz

DW %D 1619 ; G0 - 392.0 Hz

DW %D 1817 ; A0 - 440.0 Hz

DW %D 2039 ; H0 - 493.9 Hz

DW %D 2161 ; C1 - 523.3 Hz

|

Ugrađena Flash memorija

Na razvojnu pločicu ULX2S ugrađena je Flash memorija kapaciteta 4 MB

koja je s FPGA sklopom povezana putem sučelja Serial Peripheral Interface (SPI).

U FRISC SoC sustavu registri modula koji radi kao SPI

serdes dostupni

su na adresi 0xFFFFFF30.

Primjer: program koji započinje novu SPI transakciju prema Flash memoriji,

šalje naredbu za slijedno čitanje bloka podataka s adrese 0, te u petlji

dohvaća prvih 512 byteova s Flash memorije koje ispisuje na serijsko sučelje.

Napomena: program koristi rutinu PUTCHAR i pripadajuće definicije vezane

za asinkrono serijsko sučelje.

IO_SPI_FLASH EQU ffffff30 ; half, RW

MOVE IO_SPI_FLASH, R1

CALL SPI_START_TRANSACTION

MOVE 0b, R0 ; SPI Flash CMD 0x0b: high-speed read

CALL SPI_BYTE

MOVE 0, R0 ; SPI Flash read addr, bits 23..16

CALL SPI_BYTE

MOVE 0, R0 ; SPI Flash read addr, bits 15..8

CALL SPI_BYTE

MOVE 0, R0 ; SPI Flash read addr, bits 7..0

CALL SPI_BYTE

MOVE 0ff, R0 ; dummy byte, ignored

CALL SPI_BYTE

MOVE 200, R2 ; citaj 512 byteova sa SPI flasha

READ_LOOP

CALL SPI_BYTE

CALL PUTCHAR

SUB R2, 1, R2

JR_NZ READ_LOOP

RET

SPI_BYTE

; salji byte (u R0) na SPI port (u R1), i

; u R0 vrati byte procitan sa SPI porta

STOREB R0, (R1)

LOADB R0, (R1)

RET

SPI_START_TRANSACTION

; posalji marker za pocetak SPI transakcije

; na SPI portu (u R1); kvari R0

MOVE 080, R0

STOREB R0, (R1 + 1)

RET

|

MicroSD memorijske kartice

Utor za MicroSD karticu povezan je s FPGA sklopom signalima koji su

dostatni za komunikaciju prema protokolu SPI. U FRISC SoC sustavu

pripadajući registri modula koji radi kao SPI

serdes dostupni su na

adresi 0xFFFFFF34. Međutim, postupak inicijalizacije

i daljnja komunikacija s MicroSD karticama

bitno su složeniji od komunikacije s ugrađenom

Flash memorijom, zbog čega se preporuča za takve primjene koristiti

već gotove biblioteke, koje su najčešče implementirane u programskim

jezicima više razine, npr.

FATFS ili

Petit FATFS.

IO_SPI_SDCARD EQU ffffff34 ; half, RW

|

Priključi za proširenje

Ukupno 29 priključaka za proširenje na DIL priključnicama mogu raditi

bilo kao ulazi ili kao izlazi. Način rada pojedinog priključka podešava

se postavljanjem pripadajućeg bita registra IO_GPIO_CTL u nulu, čime

se odabire ulazni način rada, ili jedinicu, čime priključak postaje

aktivni izlaz. Primjer konfiguriranja priključka j2(2) kao izlaza,

te generiranje pulsirajućeg signala frekvencije cca. 3 Hz

na istom izlazu u petlji:

IO_GPIO_DATA EQU ffffff00 ; word, RW

IO_GPIO_CTL EQU ffffff04 ; word, WR

MOVE 10000, R4 ; bitmask 0x10000 -> pin j2(2)

STORE R4, (IO_GPIO_CTL) ; konfiguriraj j2(2) kao izlaz

MOVE 20, R4 ; izvedi petlju 32 puta

LOOP

XOR R1, 10000, R1

STORE R1, (IO_GPIO_DATA)

MOVE 40000, R2 ; unutarnja petlja za kasnjenje

DELAY SUB R2, 1, R2

JR_NZ DELAY

SUB R4, 1, R4

JR_NZ LOOP

RET

|

Veza između priključaka na DIL priključnicama i bitova GPIO modula

vidljiva je iz VHDL opisa njihovog povezivanja:

j1_2 <= R_gpio_out(0) when R_gpio_ctl(0) = '1' else 'Z';

j1_3 <= R_gpio_out(1) when R_gpio_ctl(1) = '1' else 'Z';

j1_4 <= R_gpio_out(2) when R_gpio_ctl(2) = '1' else 'Z';

j1_8 <= R_gpio_out(3) when R_gpio_ctl(3) = '1' else 'Z';

j1_9 <= R_gpio_out(4) when R_gpio_ctl(4) = '1' else 'Z';

j1_13 <= R_gpio_out(5) when R_gpio_ctl(5) = '1' else 'Z';

j1_14 <= R_gpio_out(6) when R_gpio_ctl(6) = '1' else 'Z';

j1_15 <= R_gpio_out(7) when R_gpio_ctl(7) = '1' else 'Z';

j1_16 <= R_gpio_out(8) when R_gpio_ctl(8) = '1' else 'Z';

j1_17 <= R_gpio_out(9) when R_gpio_ctl(9) = '1' else 'Z';

j1_18 <= R_gpio_out(10) when R_gpio_ctl(10) = '1' else 'Z';

j1_19 <= R_gpio_out(11) when R_gpio_ctl(11) = '1' else 'Z';

j1_20 <= R_gpio_out(12) when R_gpio_ctl(12) = '1' else 'Z';

j1_21 <= R_gpio_out(13) when R_gpio_ctl(13) = '1' else 'Z';

j1_22 <= R_gpio_out(14) when R_gpio_ctl(14) = '1' else 'Z';

j1_23 <= R_gpio_out(15) when R_gpio_ctl(15) = '1' else 'Z';

j2_2 <= R_gpio_out(16) when R_gpio_ctl(16) = '1' else 'Z';

j2_3 <= R_gpio_out(17) when R_gpio_ctl(17) = '1' else 'Z';

j2_4 <= R_gpio_out(18) when R_gpio_ctl(18) = '1' else 'Z';

j2_5 <= R_gpio_out(19) when R_gpio_ctl(19) = '1' else 'Z';

j2_6 <= R_gpio_out(20) when R_gpio_ctl(20) = '1' else 'Z';

j2_7 <= R_gpio_out(21) when R_gpio_ctl(21) = '1' else 'Z';

j2_8 <= R_gpio_out(22) when R_gpio_ctl(22) = '1' else 'Z';

j2_9 <= R_gpio_out(23) when R_gpio_ctl(23) = '1' else 'Z';

j2_10 <= R_gpio_out(24) when R_gpio_ctl(24) = '1' else 'Z';

j2_11 <= R_gpio_out(25) when R_gpio_ctl(25) = '1' else 'Z';

j2_12 <= R_gpio_out(26) when R_gpio_ctl(26) = '1' else 'Z';

j2_13 <= R_gpio_out(27) when R_gpio_ctl(27) = '1' else 'Z';

j2_16 <= R_gpio_out(28) when R_gpio_ctl(28) = '1' else 'Z';

|

Iz korisničkih programa može se pozvati nekoliko korisnih rutina za

pretvorbu podataka između binarnog i heksadekadskog zapisa, te za

ispis i čitanje znakova sa serijskog (USB) sučelja. Deklaracije adresa

za pozivanje potprograma te njihovi argumenti i specifičnosti

navedeni su u sljedećem primjeru, kojim je ujedno ilustriran i način

pozivanja potprograma u jednostavnoj petlji za ispis brojeva:

GETCHAR EQU 03fe0 ; u R0 vrati char procitan s RS232, blokira

PUTCHAR EQU 03fe4 ; ispisi char u R0, kvari R1

PUTHEX EQU 03fe8 ; ispisi char u R0 kao hex, kvari R0, R1

PUTHEX_W EQU 03fec ; ispisi word u R0 kao hex, kvari R0, R1, R2

PUTS EQU 03ff0 ; ispisi string s adrese u R0, kvari R1

ISHEX EQU 03ff4 ; u R0 vrati 1 ako je R1 hex char, inace 0

HEX2BIN EQU 03ff8 ; u R0 vrati dekodirani hex char iz R1

MOVE 0abc0, R6 ; akumulator - pocetna vrijednost

MOVE 4, R5 ; brojac: petlju izvedi 4 puta

LOOP

ADD R6, 2, R6 ; broji parne brojeve

MOVE R6, R0 ; ispisi word iz R6 u heksadekadskom formatu

CALL PUTHEX_W

MOVE 0d, R0 ; ASCII CR (povratak na pocetak retka)

CALL PUTCHAR

MOVE 0a, R0 ; ASCII LF (novi redak)

CALL PUTCHAR

SUB R5, 1, R5 ; smanji brojac

JR_NZ LOOP

RET

|

Izvođenjem primjera na zaslonu terminala dobit će se ovakav odziv:

FRISC @ 00000000>~>Local file name? primjer.p

FRISC @ 00000030>j0

Booting at 00000000

0000ABC2

0000ABC4

0000ABC6

0000ABC8

FRISC @ 00000000>

|

Izvorni kod bootloadera dostupan je ovdje:

frisc_boot.asm